# Dario Narducci, University of Milano Bicocca, Italy

Top-down and bottom-up approaches for SiNWs based micro-TEGs

# **Outline**

- Why «all silicon» TEGs

- Demo applications

- Redundancy

- Thermoelectric generators:

- bottom-up

- top-down

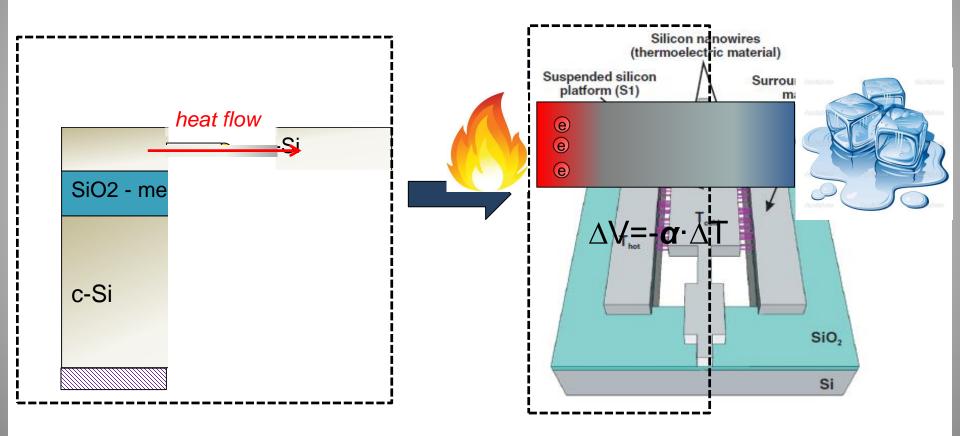

- Why microenergy solutions: Replace primary batteries (cost, environmental, deployment flexibility issues) by harvesters + secondary batteries

- Why Silicon materials and architectures: tap into the micronanoelectronics field which is an enabling technology, dealing with miniaturised and high density features (3D) implementations, offering economy of scale (serve mass markets) and the possibility of integration and addition of control and smartness

- Why such applications: complementary microenergy testbeds from the perspective of silicon benefits ('smaller is better', 'cheaper is better') and availability of energy harvesting sources

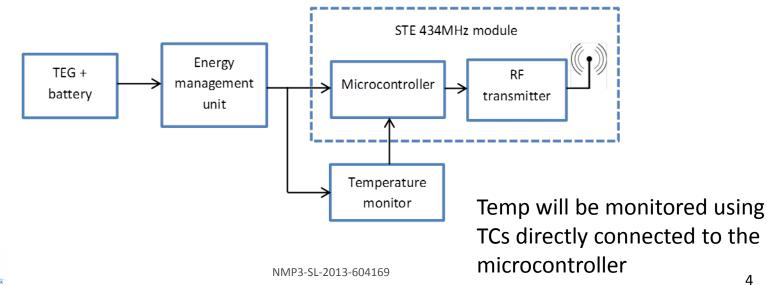

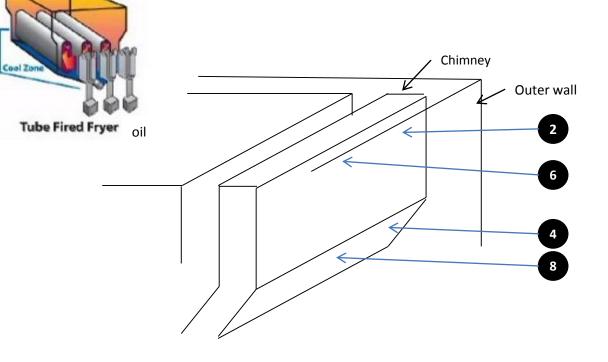

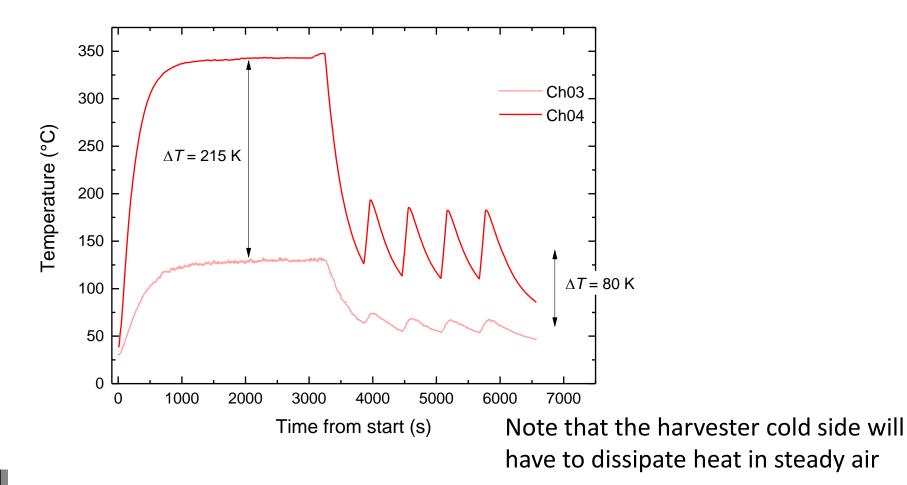

Industrial fryers are gas-powered, unplugged industrial appliances.

EC regulations require oil quality to be monitored. A log of oil temperature vs. time would fulfil this obligation.

Thermal harvester will supply the power needed to monitor oil temp and to transmit data through a wireless connection to a remote data logging system without the burden of wiring the fryer to the electric net.

# Application scenario: Industrial Fryers

Hot and cold spots needed to thermal harvesters were located at chimney walls.

CSIC (Barcelona) and IREC (Barcelona)

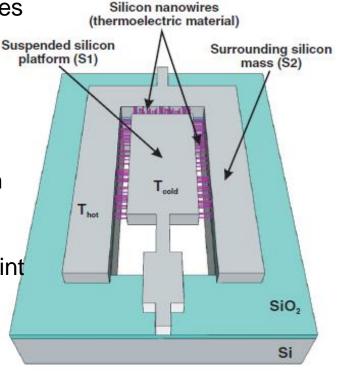

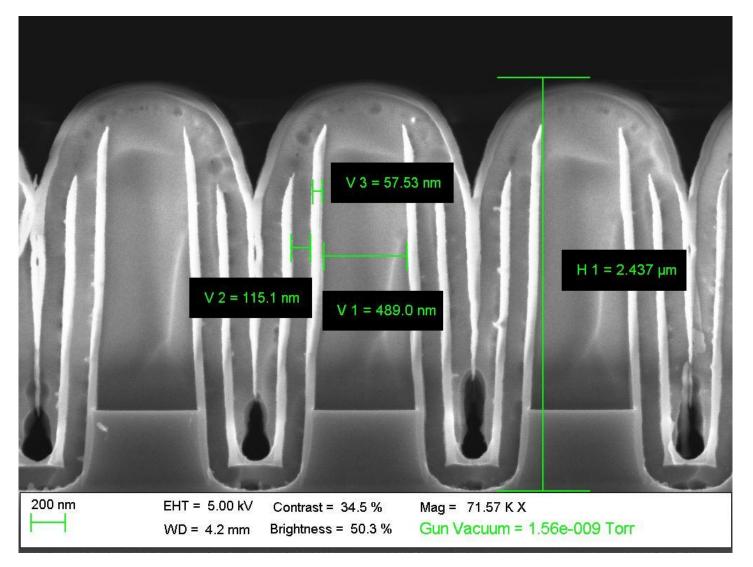

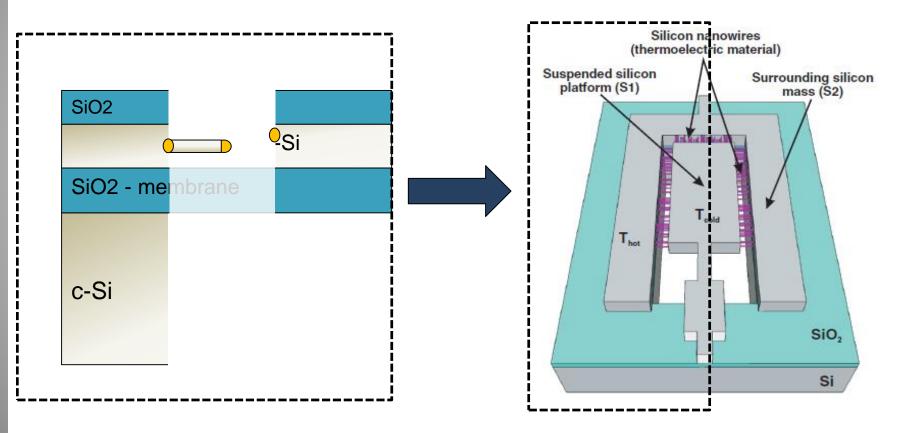

# THE BOTTOM UP STRATEGY

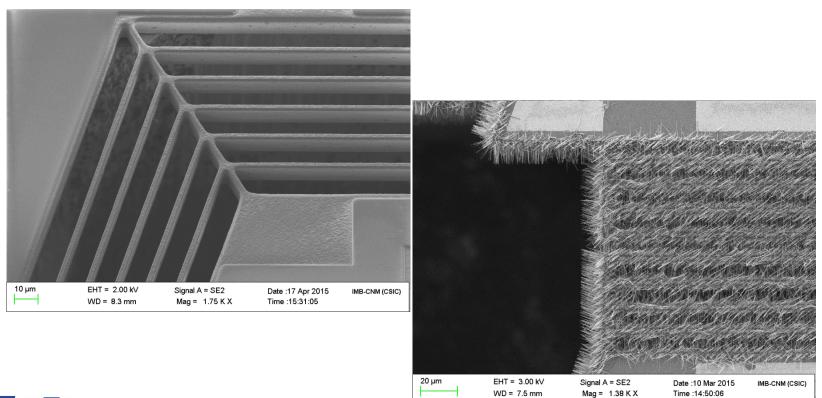

- Deposition of gold nanoparticles on device trenches by Galvanic Displacement

- Growth of silicon nanowires on CVD by VLS synthesis

- Removal of membrane and passivation oxide with HF

- Drying of the device with nanowires by Critical Point Drying/Freeze Drying

Dávila et al, J. Elect. Mat., Vol. 40, No. 5, 2011

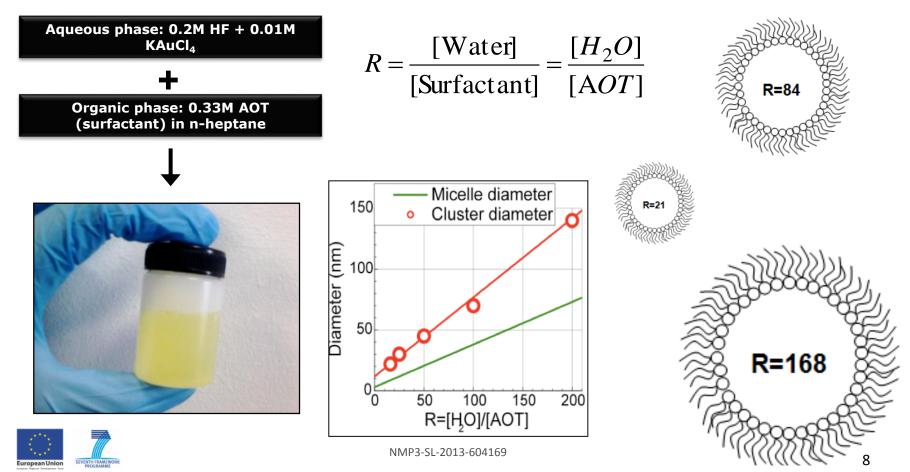

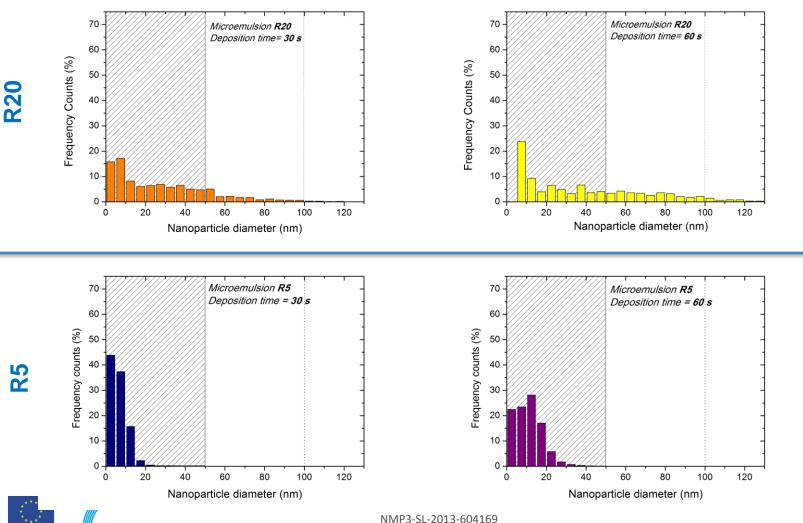

Microemulsion Galvanic Displacement

#### 1 – Microemulsions are prepared.

Gao et al, J. Am. Chem. Soc. 127, 4574 (2005)

- 1 Several microemulsions with different R values are prepared.

- 2 Devices are dipped in HF in order to remove native oxide from trenches

- 3 Devices are **dipped in microemulsions** during a controlled dipping time. Gold NPs are formed

- 4 Devices are **annealed** to remove the remaining surfactant

| Parameter                | Value       |

|--------------------------|-------------|

| S <sub>sinw</sub>        | 1.46e-3 V/K |

| ρ <sub>siNW</sub>        | 13.5 Ωcm    |

| k <sub>sinw</sub>        | 50 W/mK     |

| L <sub>siNW</sub>        | 10 - 90 μm  |

| r <sub>AMBIENT</sub>     | 76.4 K/W    |

| <b>R</b> <sub>PATH</sub> | 50 Ω        |

| $\Delta T_{TE}$          | 100 K       |

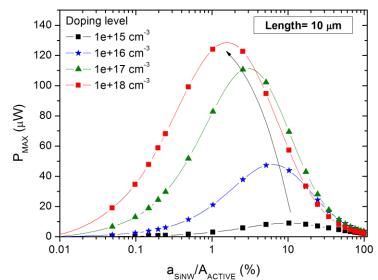

Effect of SiNW doping level - Optimized device

Effect of low doping level of SiNW - Non-optimized device

EVENTH FRAMEW

uropean Unior

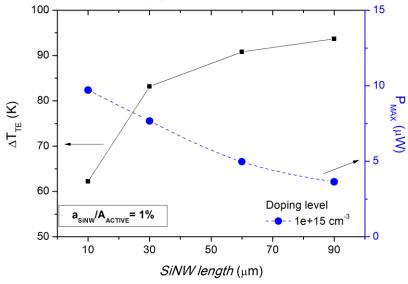

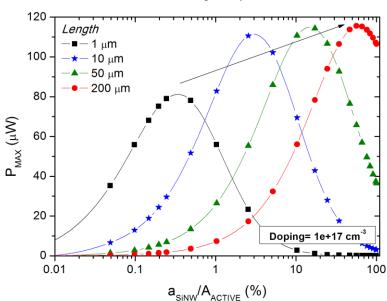

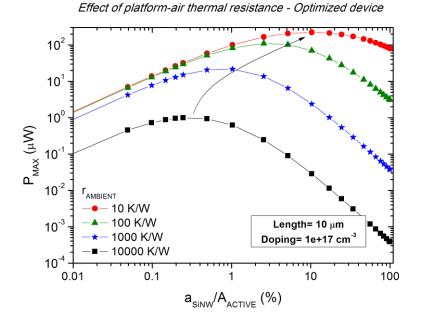

Effect of SiNW length - Optimized device

#### *ining the device I-V curve* Doping level effect on device performance SiNW density effect on device performance

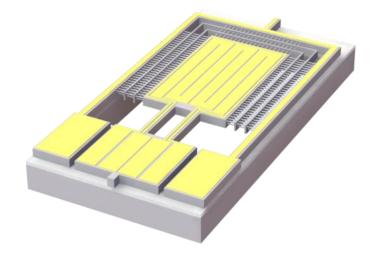

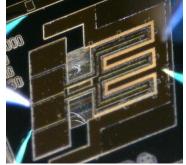

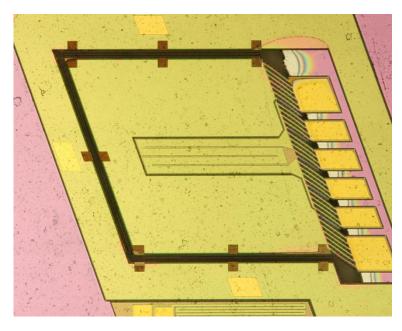

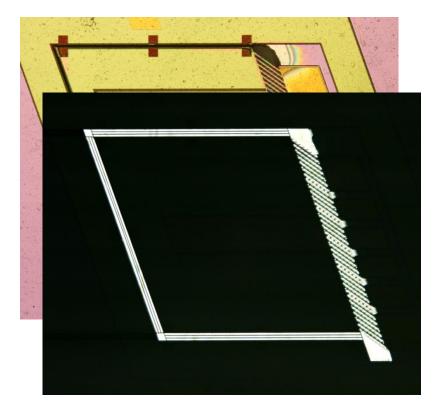

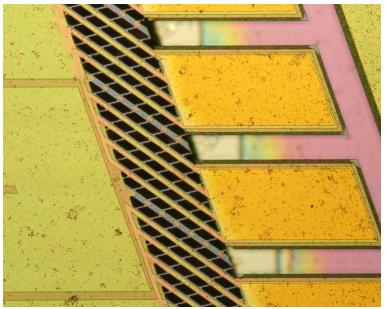

• Multiple configurations, for pure harvesting or test purposes, with built-in heaters for characterization with controlled gradients.

• Series and parallel connections of multiple devices.

- different length of membranes.

- different numbers of trenches (1 to 4) to be filled by Si NWs.

- bridges in place of membranes.

- no temporary Si bulk supports.

- prefixed percentages of bulk Si.

IMM-CNR (Bologna) and Univ. of Milano Bicocca

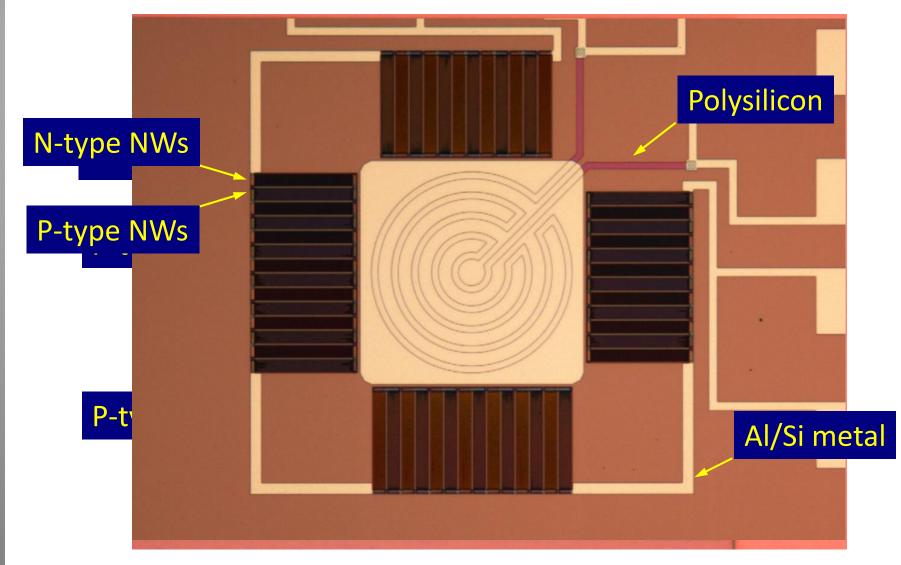

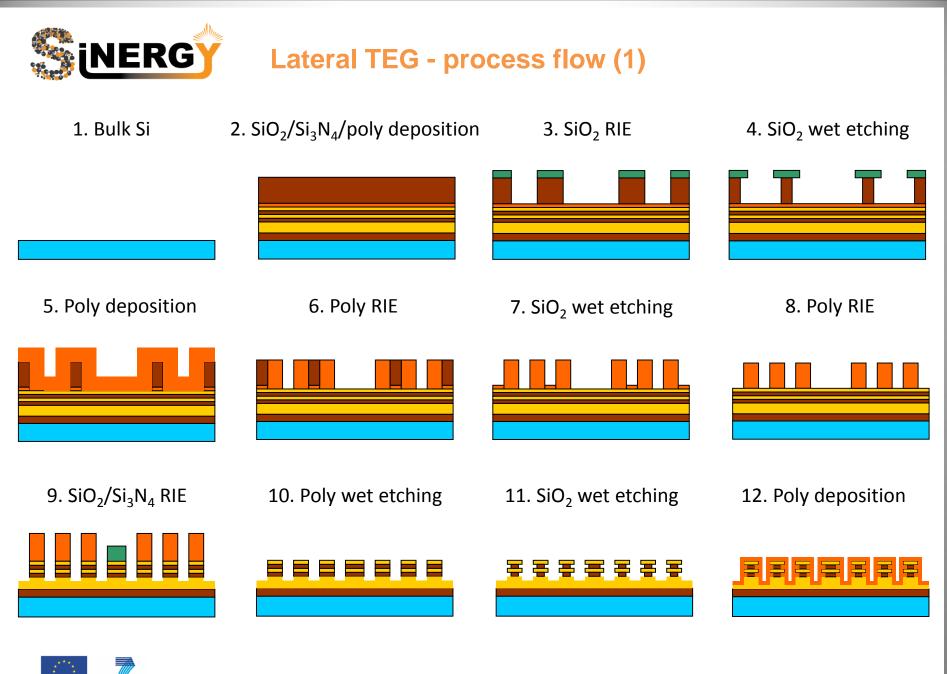

# **THE TOP-DOWN APPROACH**

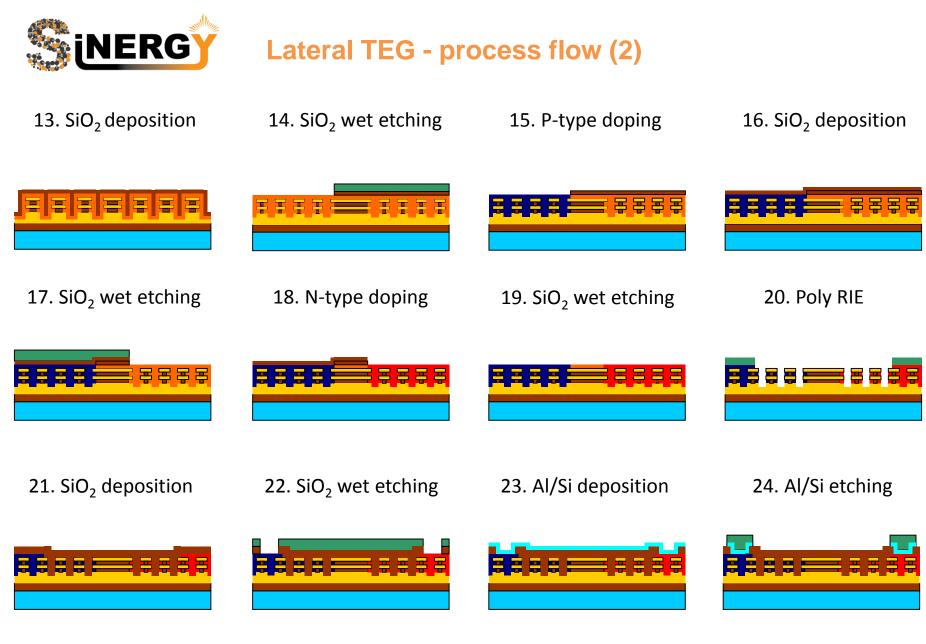

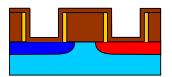

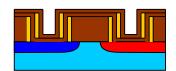

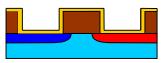

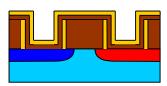

### Lateral TEG - process flow (3)

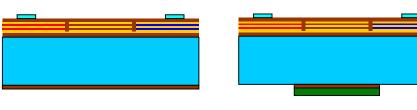

25. Wafer with NWs

26.  $SiO_2/Si_3N_4$  RIE

#### 27. Wafer bonding

28. Si DRIE

29. SiO<sub>2</sub> etching

30. Si DRIE

### 31. Wafer bonding

32. Glass dicing

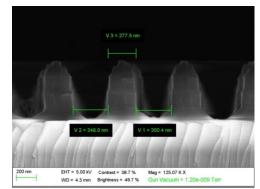

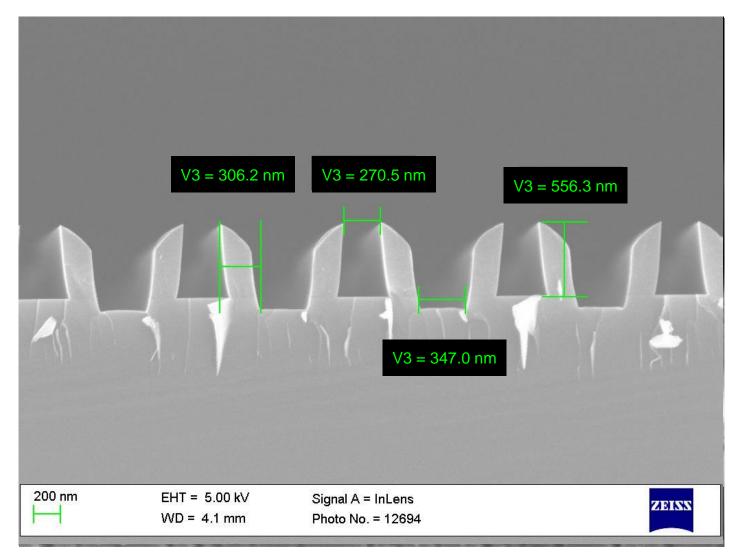

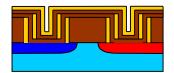

# **INERGY** Lateral TEG – Spacers for high-density NWs

### Lateral TEG – SiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub> templates for NWs

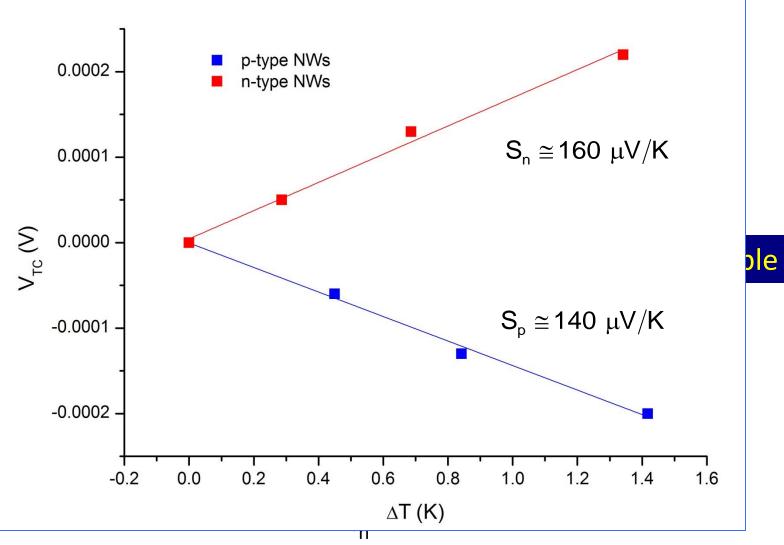

### **NERGY** Lateral TEG – Seebeck measurements on NWs

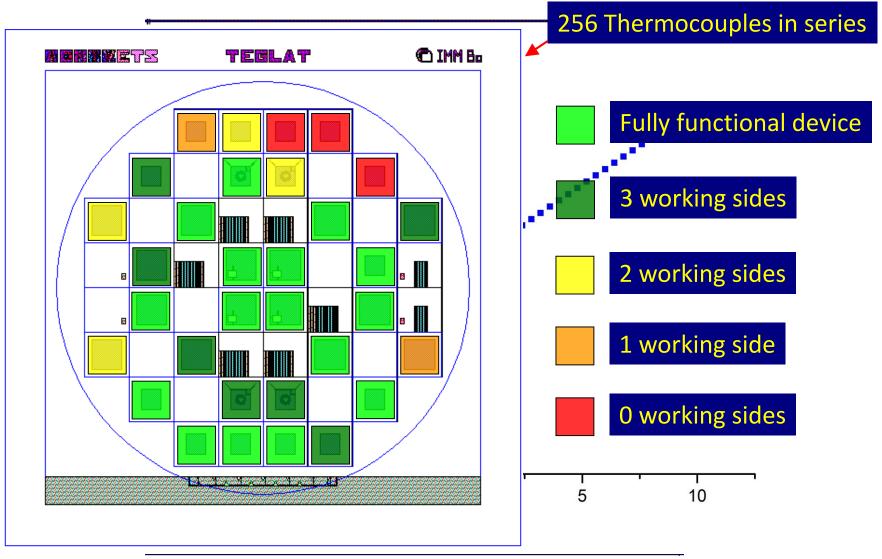

## **INERGY** Lateral TEG – Yield test on TEG prototypes

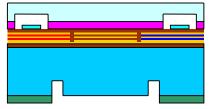

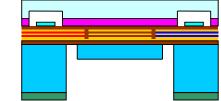

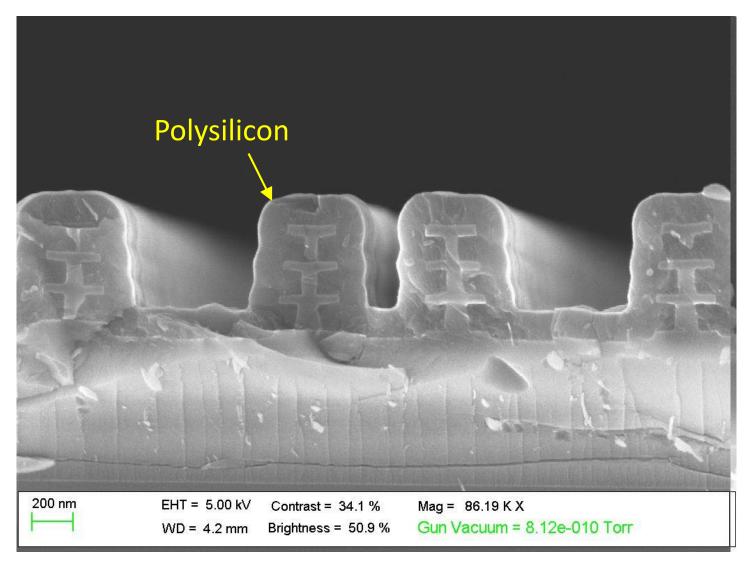

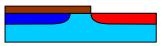

### **Vertical TEG – Process flow**

1. Si substrate

4. Thick SiO<sub>2</sub> deposition

7.  $Si_3N_4$  etchback

10.  $Si_3N_4$  etchback

- 2. P-type doping

- 5. SiO<sub>2</sub> RIE

8.  $SiO_2$  deposition

11.  $SiO_2$  deposition

3. N-type doping

6. Si<sub>3</sub>N<sub>4</sub> deposition

9.  $Si_3N_4$  deposition

12.  $Si_3N_4$  deposition

## Summary

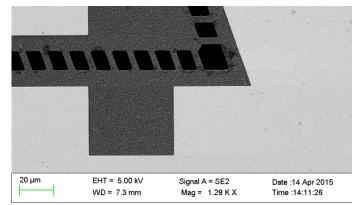

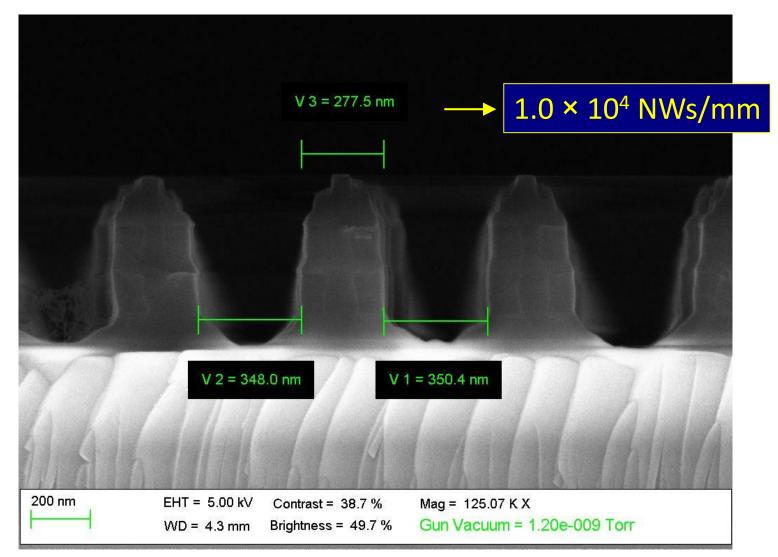

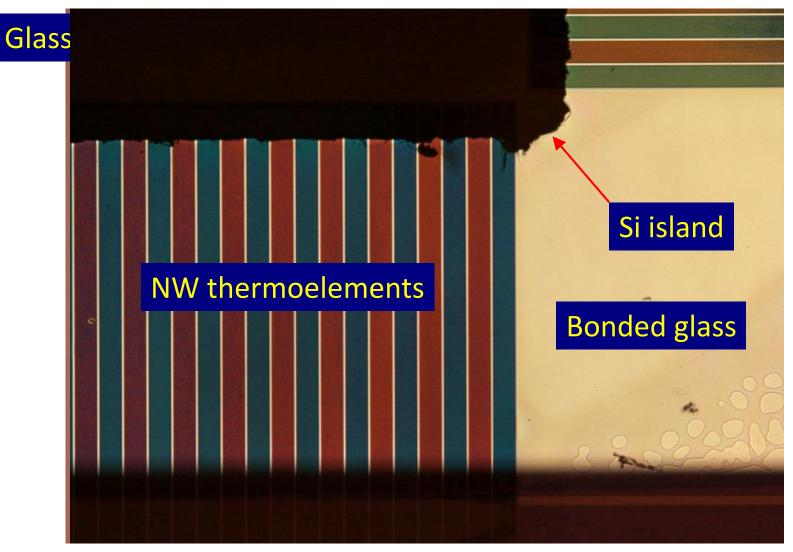

- Lateral NW arrays with linear density of 1.0×10<sup>4</sup>/mm have been obtained.

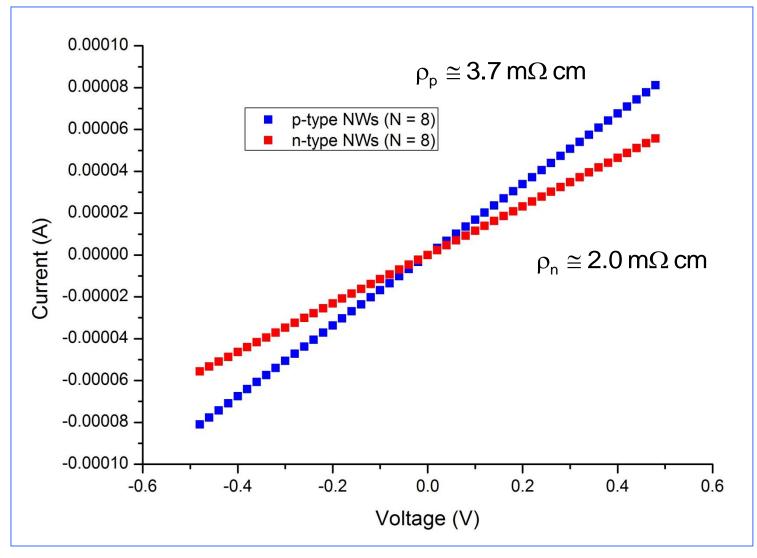

- On the high-density lateral NWs, electrical resistivity values around 2.0 m $\Omega$  cm with n-type doping and 4.0 m $\Omega$  cm with p-type doping have been achieved.

- The measured Seebeck coefficient was around 150  $\mu\text{V/K}$  for both doping types.

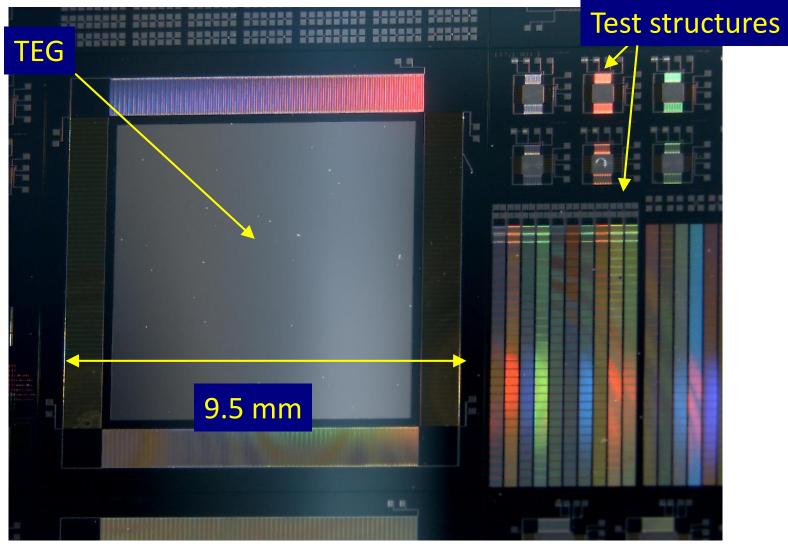

- An overall functionality above 80% has been obtained on lateral TEG prototypes in yield tests.

- The fabrication of vertical TEGs is ongoing. Early results on the fabrication of high-density templates for vertical NWS have been obtained.

# **Conclusions**

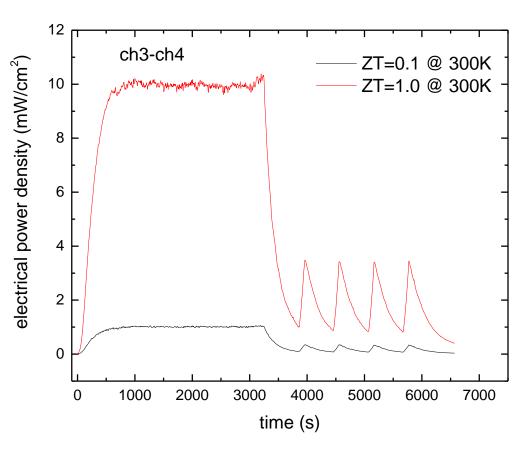

- Both top-down and bottom-up approaches to TEGs could achieve their target as of nominally available power density.

- Next targets of WP2 will be

- assembling and wiring the chips

- packaging

- testing (benchtop, simulated, and actual scenario)

### **The Thermoelectric Team**

<u>CSIC</u>: Luis Fonseca (Project leader), Carlos Calaza, Marc Salleras, Jaume Esteve, Inci Dönmez <u>IMM-CNR</u>: Alberto Roncaglia, Fulvio Mancarella <u>IREC</u>: Albert Tarancon, Alex Morata, G. Gadea, J.D. Santos

<u>Univ. of Milano Bicocca</u>: Dario Narducci, Laura Zulian, Bruno Lorenzi

sinergy-project.eu Contact: luis.fonseca@imb-cnm.csic.es

### This work was supported by FP7-NMP-2013-SMALL-7, SiNERGY (Silicon Friendly Materials and Device Solutions for Microenergy Applications), Contract n. 604169

sinergy-project.eu Contact: luis.fonseca@imb-cnm.csic.es

### **Application scenario:**

## Application scenario: Industrial Fryers

Minimal needed power estimated considering that the average input electric power required by RF module to read temp + transmit data at 3V is 3.5 to 4µW for transmission each 10 s 1.3 to 1.5µW for transmission each 60 s

Average power during pulse transmission (6 ms) is 2.7mW.

Instantaneous peak power can be up to 75mW. A large capacitor  $(22\mu F)$  will be placed after the power management unit.

Silicon friendly materials and device solutions for thermoelectric harvesting

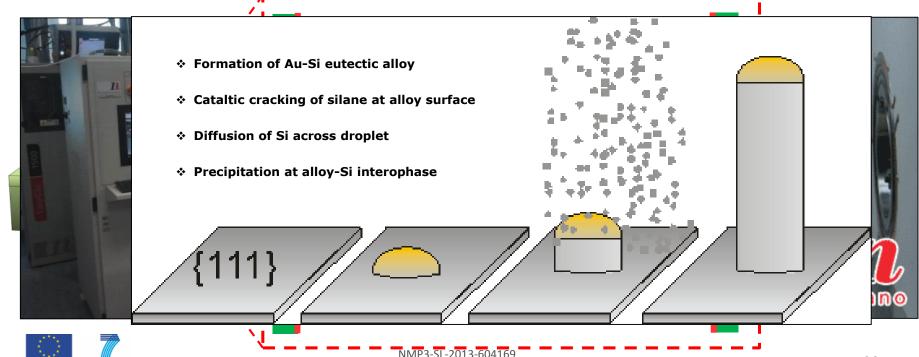

#### **CVD-VLS growth of silicon nanowires**

- 1 Devices are dipped in **HF** in order to remove thermal oxide formed druing calcination

- 2 Devices are loaded into CVD

- 3 There devices are brought to reaction conditions and exposed to silane. Silicon

nanowires are grown by VLS synthesis

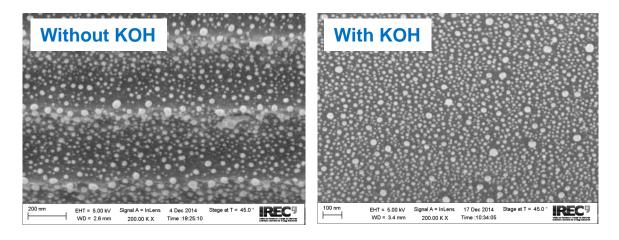

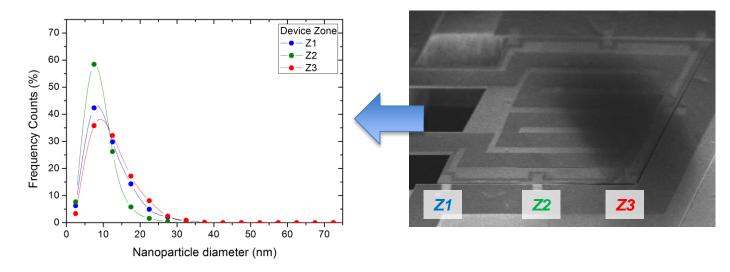

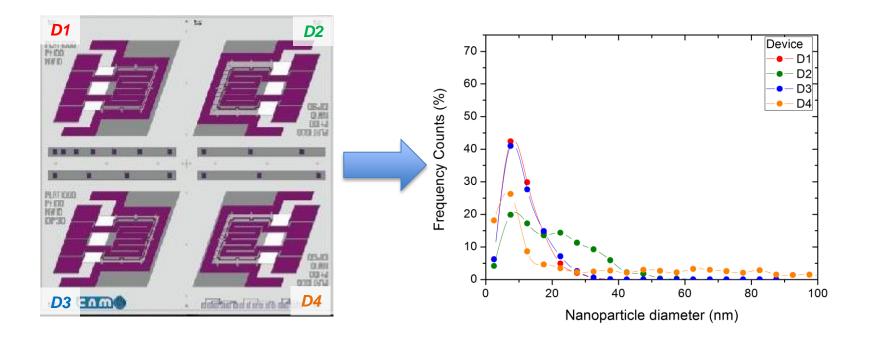

Looking for a higher control of the galvanic displacement

- 1. Analysis of the gold homogeneity in the trenches

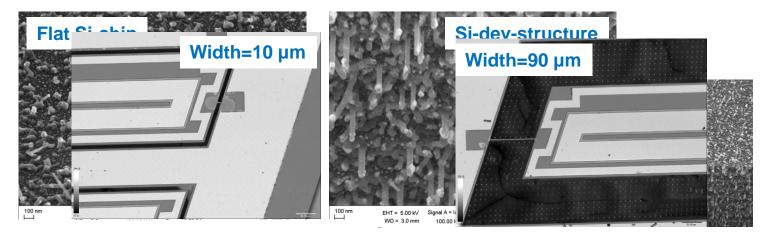

- 2. Influence of the trench width and the structure itself on the gold deposit

Looking for a higher control of the galvanic displacement

1. Analysis of the gold homogeneity in the trenches

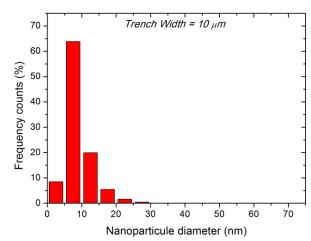

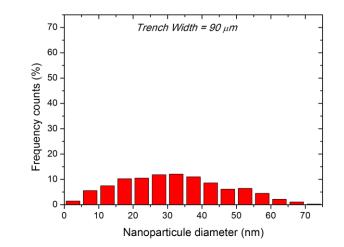

2. Influence of the trench width on the gold nanoparticle size

#### Looking for a higher control of the galvanic displacement

- 1. Analysis of the gold homogeneity in the trenches

- 2. Influence of the trench width on the gold nanoparticle size

#### Looking for a higher control of the galvanic displacement

- 1. Analysis of the gold homogeneity in the trenches

- 2. Influence of the trench width on the gold nanoparticle size

34

### **General Scheme**

#### Main steps in the fabrication process

- 1. Gold deposition Galvanic displacement

- 2. SiNW growth CVD process

- 3. *µTEG* basic thermoelectric characterization

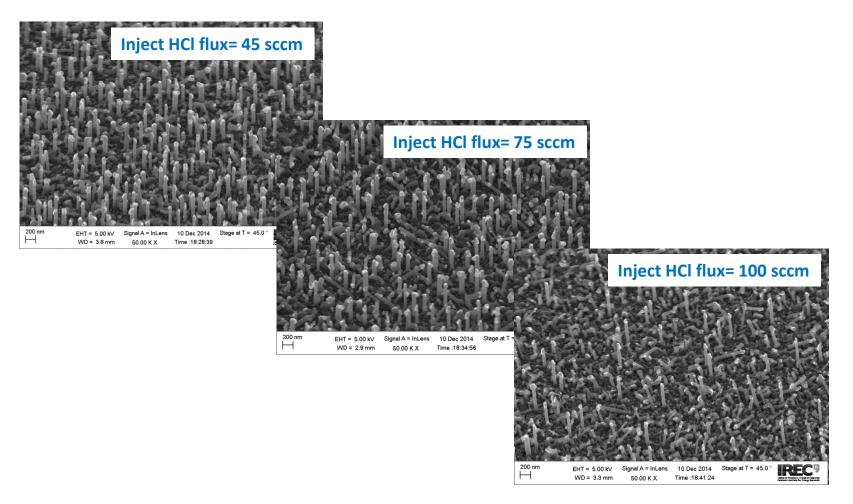

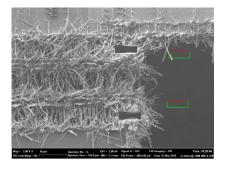

### SiNW growth – CVD process

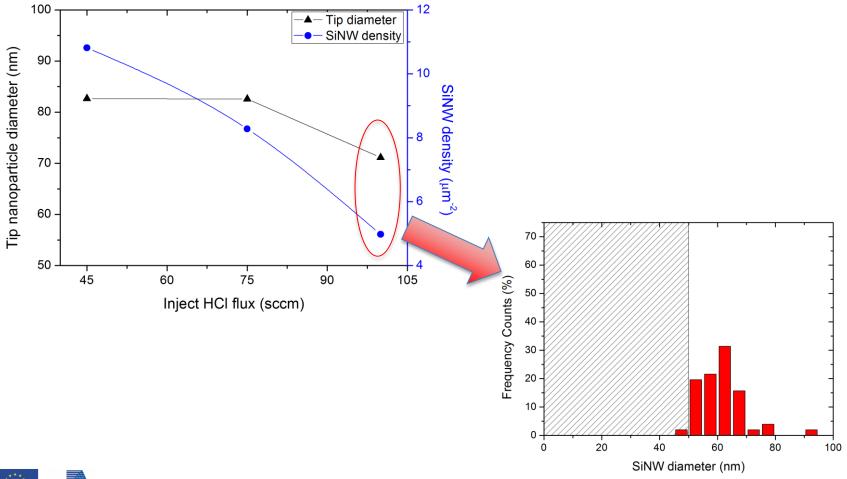

#### Control of the SiNW array characteristics

- 1. Influence of the HCl pre-inject step on array density

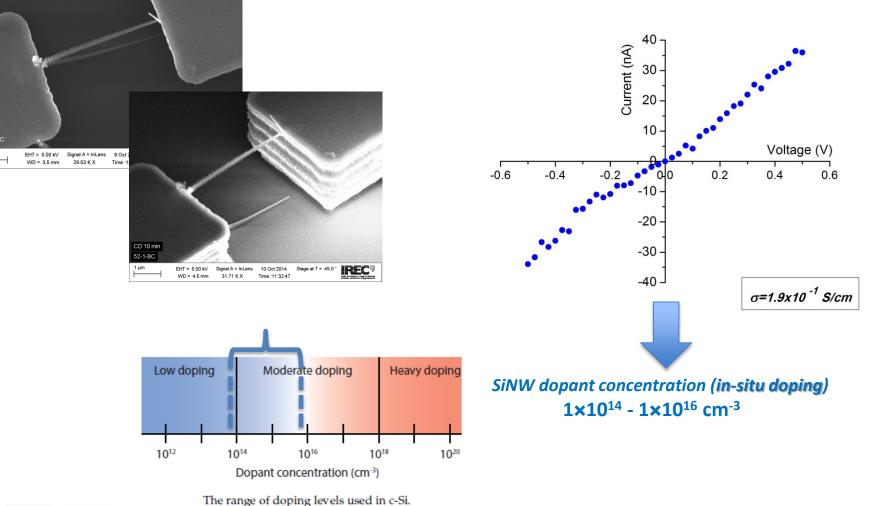

- 2. Preliminary p-doped SiNW electrical measurements

### SiNW growth – CVD process

#### Control of the SiNW array characteristics

- 1. Influence of the HCl pre-inject step on array density

- 2. Preliminary p-doped SiNW electrical measurements

### SiNW growth – CVD process

#### Control of the SiNW array characteristics

- 1. Influence of the HCl pre-inject step on array density

- 2. Preliminary p-doped SiNW electrical measurements

1 µm

### SiNW growth – CVD process

#### Control of the SiNW array characteristics

- 1. Influence of the HCl pre-inject step on array density

- 2. Preliminary p-doped SiNW electrical measurements

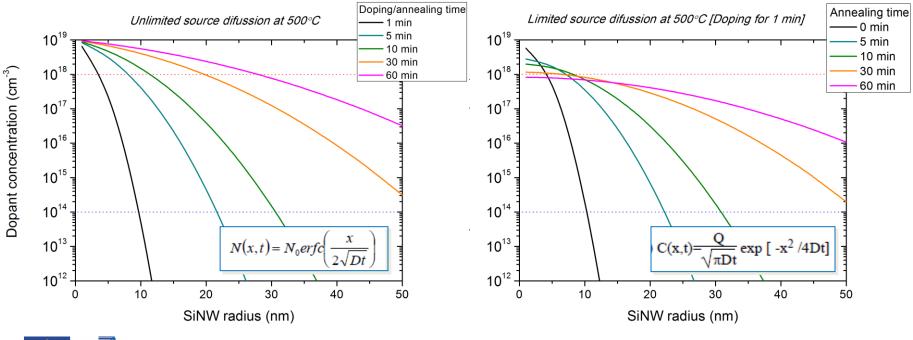

#### W. Chen et al. - J. Appl. Phys. 111, 094909 (2012) *B difussion coefficient in SiNW at 500°C - D=4.22 × 10<sup>-16</sup> cm<sup>2</sup>/s*

#### SiNW dopant concentration (ex-situ doping)

### **General Scheme**

#### Main steps in the fabrication process

- 1. Gold deposition Galvanic displacement

- 2. SiNW growth CVD process

- 3. *µTEG basic thermoelectric characterization*

### **Conclusions**

#### New results in the fabrication process at IREC

- Gold deposition

- The Au particle size distribution present high uniformity (top to bottom/along the trenches) after KOH etching and SiO<sub>2</sub> membrane elimination.

- Gold microemulsion and deposition time have to be optimized for each device structure. Nanoparticle diameter lower than critical diameter for SiNW growth (d<sub>c</sub>=50 nm) are preferable.

- SiNW growth

- Combined with small Au nanoparticles (d<d<sub>c</sub>), the HCl pre-inject flux allows to control the SiNW density.

- Preliminary electrical measurements confirm a low SiNW doping level. Ex-situ doping could lead to higher and more uniform doping levels.

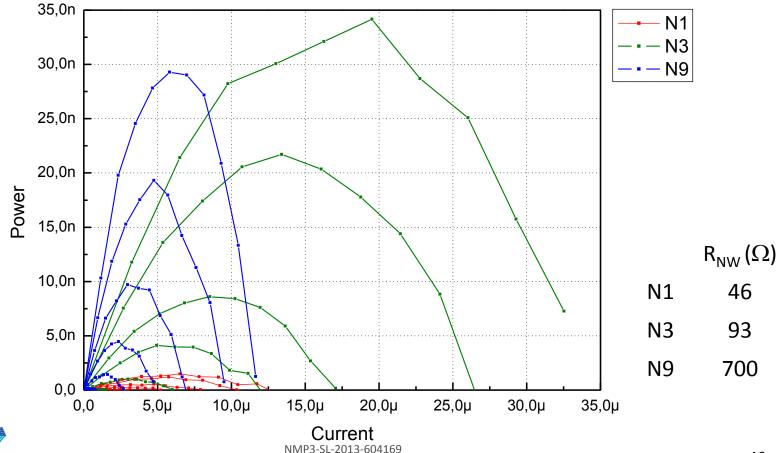

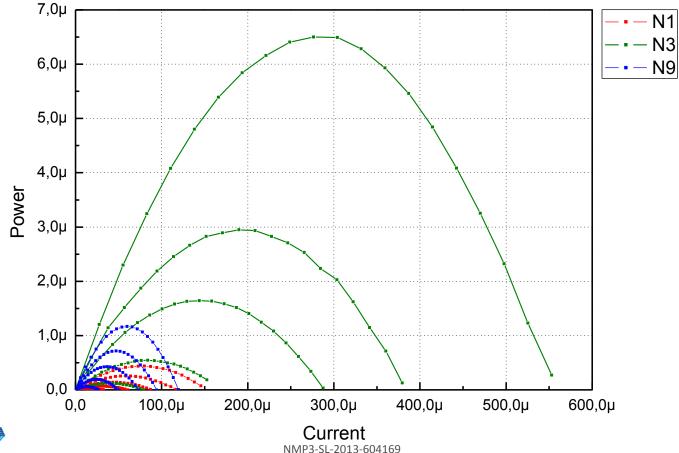

- μTEG basic characterization

- Low doping level would be responsible for low power values. Simulations confirm that a SiNW conductivity increase would lead to noticeably improve the P<sub>MAX</sub>.

- The control of the SiNW array density would have an important impact on the performance of the device.

Different SiNW properties and/or device structure characteristics will require an array density optimization.

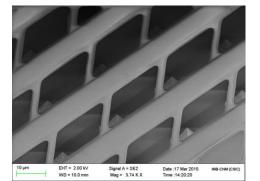

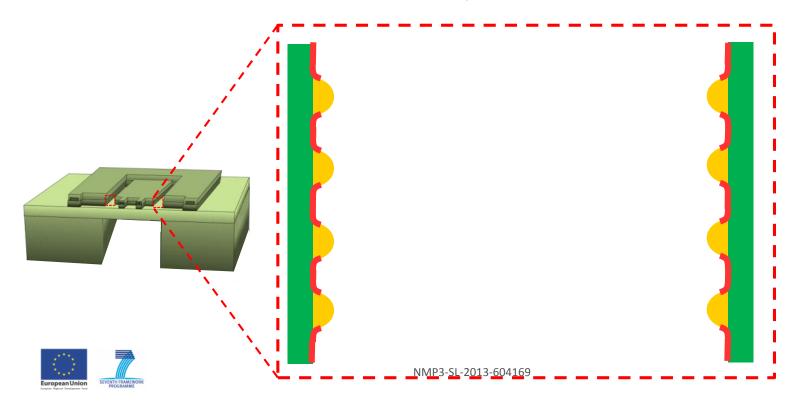

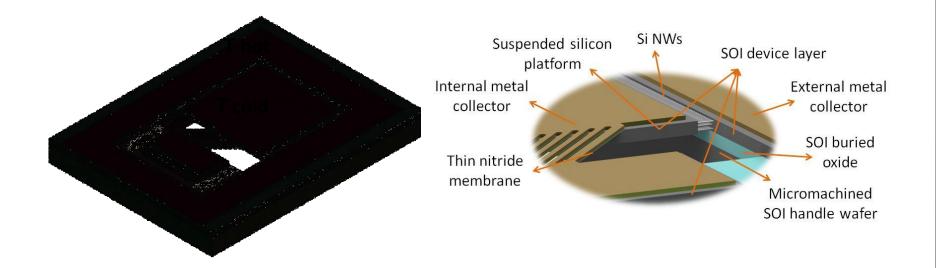

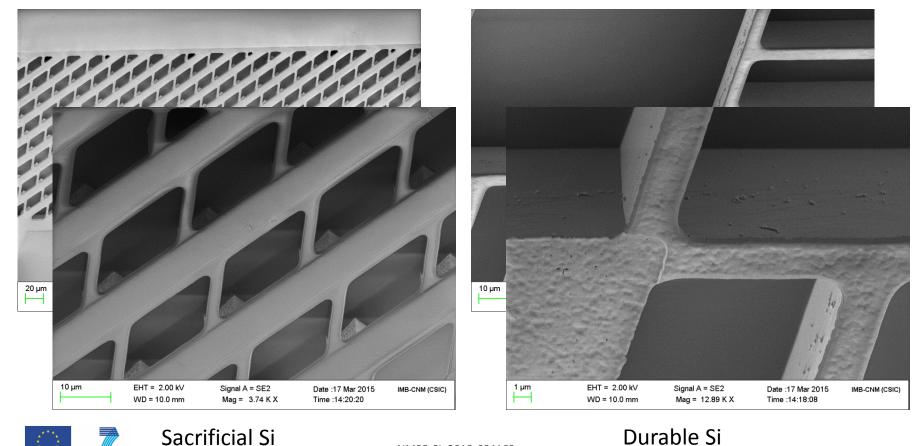

## **Bottom-up strategy – Si platforms**

# Si platforms

Sacrificial Si

NMP3-SL-2013-604169

## **Bottom-up strategy – Si platforms**

• Buried oxide removed with HF vapors after DRIE on the back side.

• Resist removed with plasma etch

## **Bottom-up strategy – Measurements**

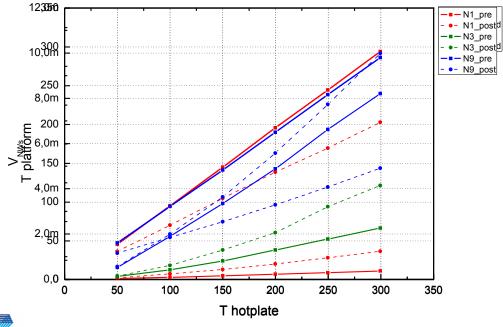

- Thermovoltage and thermopower obtained in several harvesting conditions were determined for devices with different number of NWs arrays.

- Forced convection was used to improve  $\Delta T$ .

- Silicon temporary supports were removed by FIB.

## **Bottom-up strategy – Measurements**

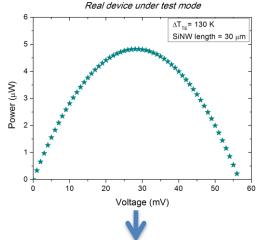

• Power curves. Harvesting mode with T of the hotplate up to 250 °C.

## **Bottom-up strategy – Measurements**

• Power curves. Test mode with  $\Delta T$  up to 100 °C.

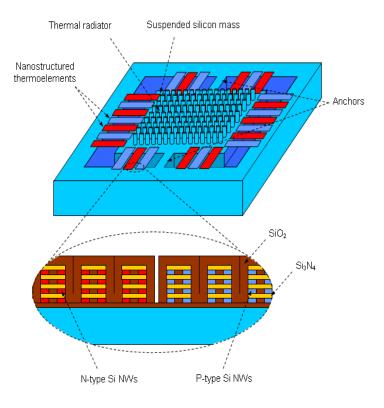

From simulation results, the following requirements have been derived for high-performance top-down TEGs:

- Use of high density NWs arrays as thermoelements in the TEGs

- Fabrication of low resistivity NWs with n and p-type doping on the same substrate

- Vacuum packaging technology for the lateral TEGs, if possible, in order to eliminate heat exchange through air

- Fabrication of TEGs with a large number of thermocouples in series in order to multiply the output voltage (important for readout)

### Lateral TEG – High-density NWs

## **NERGY** Lateral TEG – TEGs and test structures on the same wafer

## **INERGY** Lateral TEG – TEGs and test structures in vacuum

Lateral TEG – IV measurements on NWs

NERGY

## Lateral TEG – Thermopiles composed by NWs